Despite the fact that silicon is the most widely used semiconductor in electronics, new research indicates some limitations, especially in high-power applications. Bandgap is an important consideration for semiconductor-based circuits because larger bandgaps show greater benefits at high temperatures, voltages, and frequencies. Si has a bandgap of 1.12 eV, whereas silicon carbide has a bandgap of 3.2 eV. When compared to Silicon, this is nearly three times larger. SiC thus offers enhanced performance overall, increased efficiency at higher switching frequencies, and component compactness. SiC MOSFETs are employed in a variety of applications to improve the circuit’s overall electrical properties.

SiC MOSFETs have outstanding characteristics and a unipolar conduction mechanism, resulting in reduced size and improved switching performance. Furthermore, despite having the same current and voltage ratings as Si counterparts, SIC MOSFETs may be 65x smaller due to Huang’s figure-of-merits [1]. Because of the smaller size, the overall parasitic capacitance is much lower, allowing the SiC MOSFET to achieve high switching speed and low ON-state resistance. As a result, SiC-based converters with high switching frequencies for high power density could be used in hybrid/electric vehicles, solar inverters, and uninterrupted power supply.

Previous studies have found that the sizable reduction in SiC chip size is only taken into account for the active region. The fringe electric field created at the active region’s edge prevents the termination zone from scaling. This surrounds the active region and contributes to nearly optimal avalanche breakdown. A group of researchers investigated how parasitic capacitance introduced from the termination area affects switching loss in SiC MOSFETs [2]. The Chinese National Natural Science Foundation and the State Key Laboratory of Wide-bandgap Semiconductor Power Electronic Devices conducted this study.

SiC MOSFET termination region analysis

In their paper titled “Impact of Termination Region on Switching Loss for SiC MOSFET,” the researchers look at the impact of termination area on parasitic capacitances. Putting it simply, parasitic capacitance is an unavoidable capacitance that develops between parts of an electrical component or circuit because of their close proximity.

The capacitances between the SiC MOSFET’s three terminals determine the input capacitance, output capacitance, and reverse transfer capacitance. The oxide layer beneath the gate is thicker than the gate oxide layer because the electrodes physically overlap. Furthermore, because the electrodes terminals do not overlap, they contribute very little to the total capacitance. As a result, SiC MOSFETs have capacitances from the active and termination areas make up the drain-to-source terminal capacitance.

Circuit design & Architecture

The team used TCAD Sentaurus to show the working principles of parasitic capacitances during SiC MOSFET turn-on and turn-off events. TCAD Sentaurus is a sophisticated multidimensional simulator that can simulate the electrical, thermal, and optical properties of silicon-based devices. It primarily serves to develop and optimize semiconductor process technologies. The device suffers switching losses due to the overlapping of voltage (V, across the device and current (Ids) flowing through it. Channel current (Ich) is injected via the device’s gate channel to demonstrate the switching mechanism within the SiC MOSFET.

Figure 2: A circuit schematic for parasitic capacitances with a termination zone.

The resistive passage of discharging current (I term) from the capacitance introduced in the termination area (C term) through the gate channel placed in the active region discharges Gate-to-Drain capacitance (Cgd) and Active Region Capacitance (Cacti) during the Miller period of the turn-on process. The dissipative current flowing through the gate channel, or channel current (ICH), in this interval, is a mix of current flowing in the termination region (Iterm) and the discharging current of the active region capacitance, i.e. (Iacti) and the drain-to-source current (Ids ).

Instead of flowing via the gate channel during the Miller period of turn-off operation, a portion of the drain-to-source current (Ids) begins charging the capacitance placed in the active and termination regions, i.e. Cacti and Cterm, as shown in the figure below. The dissipative channel current (Ich) here eliminates the charing C term and Cacti currents, i.e. Cterm and Cacti i.e. Ich = Ids – Iacti – Iterm.

Switching Loss Modeling for SiC MOSFET

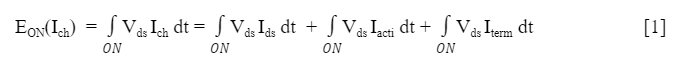

The channel current (Ich) flowing through the gate channel of the SiC MOSFET is the crucial current exhibiting switching loss during the physical study of the termination area. In contrast, the drain-to-source current is not quantifiable (Ids). As a result, the turn-on and turn-off loss expressions considering the termination region are as follows:

Combining the above equations for turn-off and turn-on loss expressions yields the following equations.

Equations 3 and 4 indicate the switching loss contribution from the measurable Ids during the on and off Miller processes. The charging and discharging of Cacti and Cterm are depicted in Equations 5 and 6. The blocking voltage that controls the energy stored in parasitic capacitances from a device’s active and terminating regions is independent of Ids.

Outputs Obtained

Figure 4 depicts a double-pulsed test using SiC MOSFETs divided into active and terminating regions to investigate the switching loss. The SiC MOSFET has rating currents of 1, 3, and 6 A with Vds = 3V and Vgs = 20.Figure 5 depicts the switching loss breakdowns of 1, 3, and 6A SiC MOSFETs at 800, 1000, and 1200V using TCAD Sentaurus simulation.

The switching loss is classified as EON (Ids), Eacti, Eterm, and EOFF (Ich ). Under varied blocking voltages and current ratings, the values of E ON (Ids), acti, and E term are comparable. However during this operation, EOFF(Ich) becomes very low. As the active region for higher current ratings expands, the fraction of overall switching loss increases. EON (Ids) and EOFF (Ich) will be bigger if a weaker gate drive is employed. Eacti and Eterm, on the other hand, are set for a given MOSFET.

Minor current travels through the gate channel during EOFF of SiC MOSFETs, creating little joule heating, but practically all of the current charges the Cacti and Cterm as displacement current. This leads to a lower EOFF value (Ich). One way to put it is as follows

From the above equation, Ig(OFF) is the gate loop discharge current during the turn-off operation. This implies that the turn-off period is substantially less than the Cacti and Cterm.

Conclusion

TCAD Sentaurus and switching loss model with termination regions are employed to replicate physical insights into the termination region. The termination zone affected switching loss, particularly for SiC MOSFETs with low current ratings. Eterm and Eacti, are intrinsic losses equal to or greater than the generally employed electric measurement estimation. These parameters are substantial components of turn-on loss. In comparison to traditional switching loss estimates, EON should contain Eterm and Eacti. During this arrangement, EOFF should omit Eterm and Eacti. The inclusion of Cterm exacerbates the under- and overestimation of EON and EOFF, respectively. Incorrect loss estimation may impact SiC MOSFET selection and applied circuit design for certain applications.

References

1A. Q. Huang. “New unipolar switching power device figures of merit.” IEEE Electron. Device Lett., Vol. 25, No. 5, pp. 298–301, May 2004.

2Li et al. “Impact of Termination Region on Switching Loss for SiC MOSFET.” IEEE Transactions on Electron Devices, Vol. 66, No. 2, pp. 1026–1031, February 2019, doi: 10.1109/TED.2018.2888995.